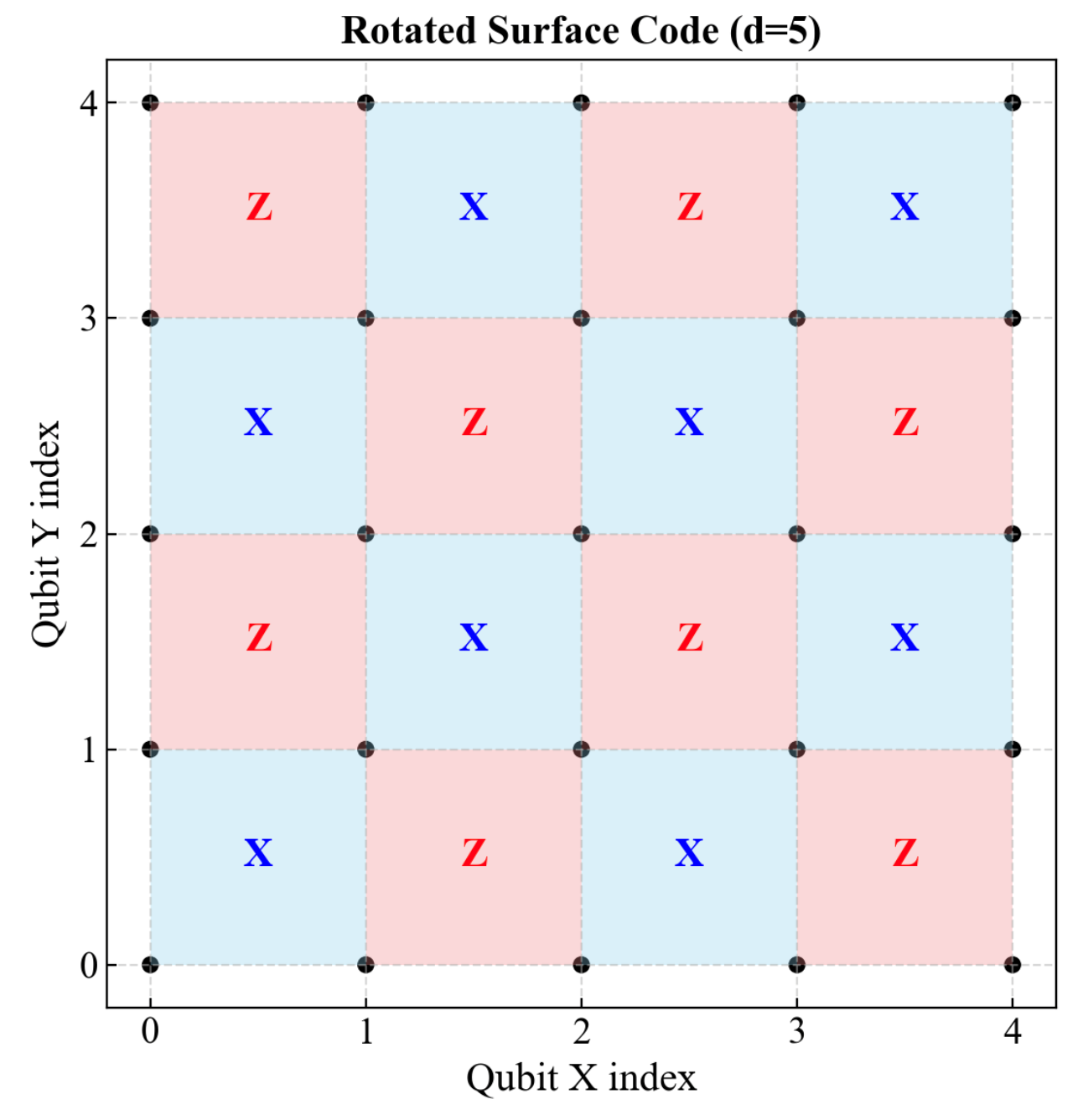

Fig.1. A rotated surface code patch with d = 5. Z and X denote the star and Plaquette operators.

Digital-Analog Quantum Error Correction

Realizing early quantum error correction

16.07.2025

Quantum Error Correction (QEC) has rapidly shifted from a theoretical necessity to a core part of experimental roadmaps. Companies like QuEra and Pasqal are already demonstrating QEC primitives with neutral atoms (Link), while Quantinuum has showcased logical qubit teleportation using trapped-ions (Link). Google has demonstrated its Willow superconducting processor’s surface-code memories up to distance-7 Google Research.

These advances are significant, but they underlie a critical limitation: the substantial overhead required to scale quantum error correction. The number of physical qubits per logical qubit grows quadratically often exceeding 100 qubits for a single logical qubit leaving current chips with capacity for only one or two logical qubits at best.

At Kipu Quantum, we believe the time is right to bridge QEC protocols with the physical capabilities of today’s quantum hardware. Through Digital-Analog Quantum Error Correction (DAQEC), we’re pioneering a faster, and hardware-specific path to logical fidelity and we’re inviting the hardware ecosystem to join us. We develop universal and scalable quantum computing solutions for industry use cases at quantum-advantage level with hardware- and application-specific adaptations to smoothly run along the roadmap of each quantum hardware provider.

The Scalability Challenge in QEC

Quantum Error Correction (QEC) is no longer theoretical but a practical necessity. But, as we push toward fault-tolerant quantum computing, one challenge persists: scalability. To reach logical error rates compatible with large-scale algorithms, we need:

- Thousand(s) of physical qubits per logical qubit

- Deep circuit layers that stretch coherence times and exceed control budgets

- QEC cycles that become slower and more error prone as code distance increases

These requirements quickly outpace what near-term hardware can support. Take the well-known example from Google’s 2023 experiments: their Sycamore processor successfully demonstrated a distance-5 surface code with a logical error rate below threshold, marking a key milestone. However, each QEC cycle took nearly one microsecond, already approaching the limits of qubit coherence and control latency. Scaling to larger code distances without a new architectural strategy, one that reduces depth or qubit overhead becomes increasingly impractical.

DAQEC: A path to scalable quantum error correction

DAQEC extends the principles of digital-analog quantum computing (see here) to the domain of fault-tolerant quantum error correction. In such protocols, circuit decompositions with layers of two-qubit and single-qubit gates are replaced with a compact sequence of global or multi-qubit analog entangling blocks interleaved with single-qubit or two-qubit digital gates. This leads to shallow circuits in simulation tasks, as shown for example by using global Mølmer-Sørensen, XX or ZZ type gates: Link.

Within this paradigm, we obtained that the rotated surface code (Fig.1) Hamiltonian along with its counterdiabatic (CD) correction can be encoded using digital-analog schemes natively in grid-based superconducting circuits (see our last blog for higher order CD driving: Link)

In our latest benchmarking study, with a hardware specific scheme, we tested DAQEC using the native exchange interactions (as available in superconducting processor like Google's digital-analog quantum simulator) as the analog blocks and iSWAP digital gates, obtaining that DAQEC enables:

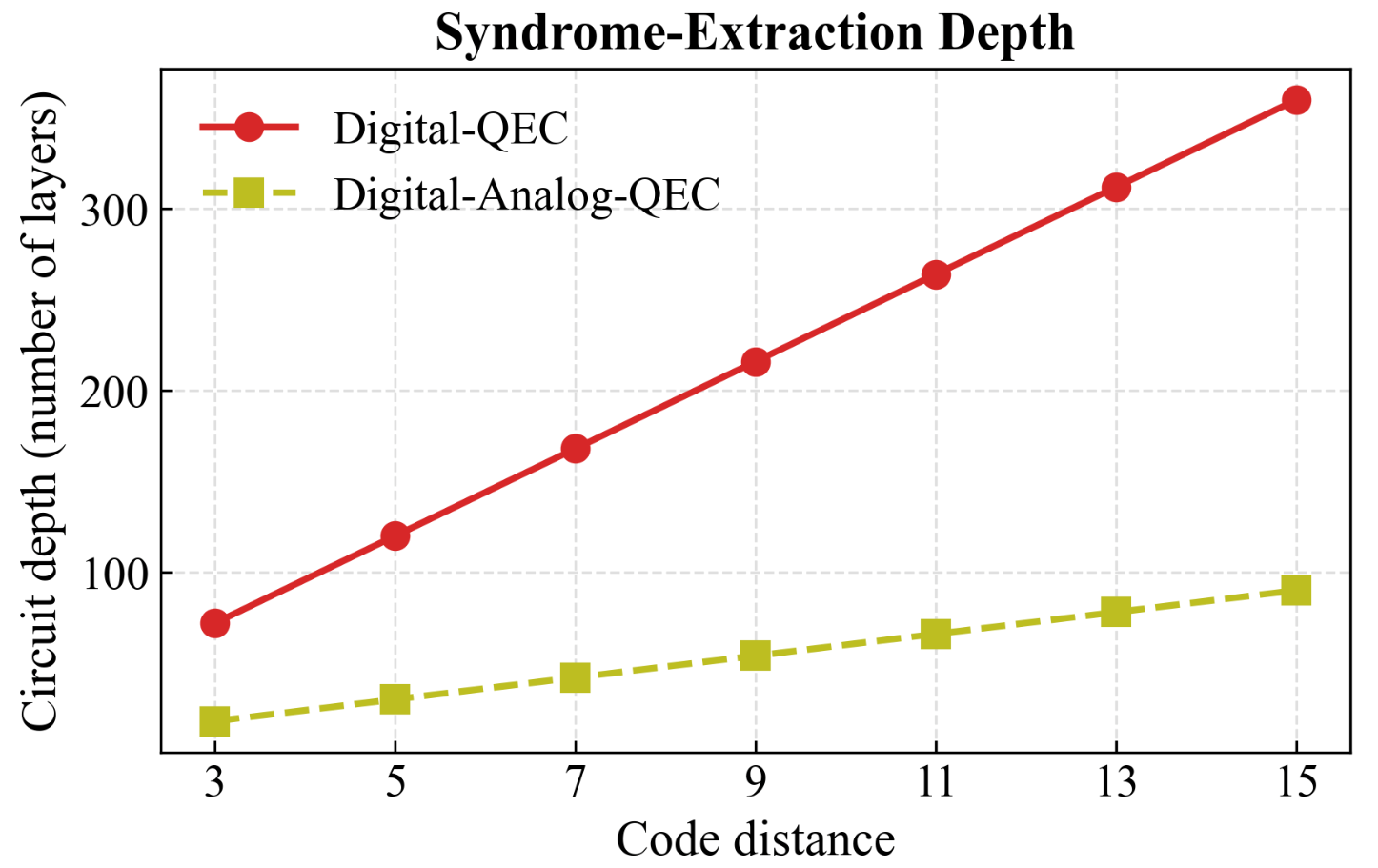

- 4× reduction in circuit depth (Fig. 2).

- Up to 2× reduction in physical qubits per logical qubit for the same target error rate when using Kipu’s DAQEC scheme.

- Improved logical error suppression at higher code distances.

- Compatibility with grid-based superconducting circuits, neutral atoms and trapped-ion devices.

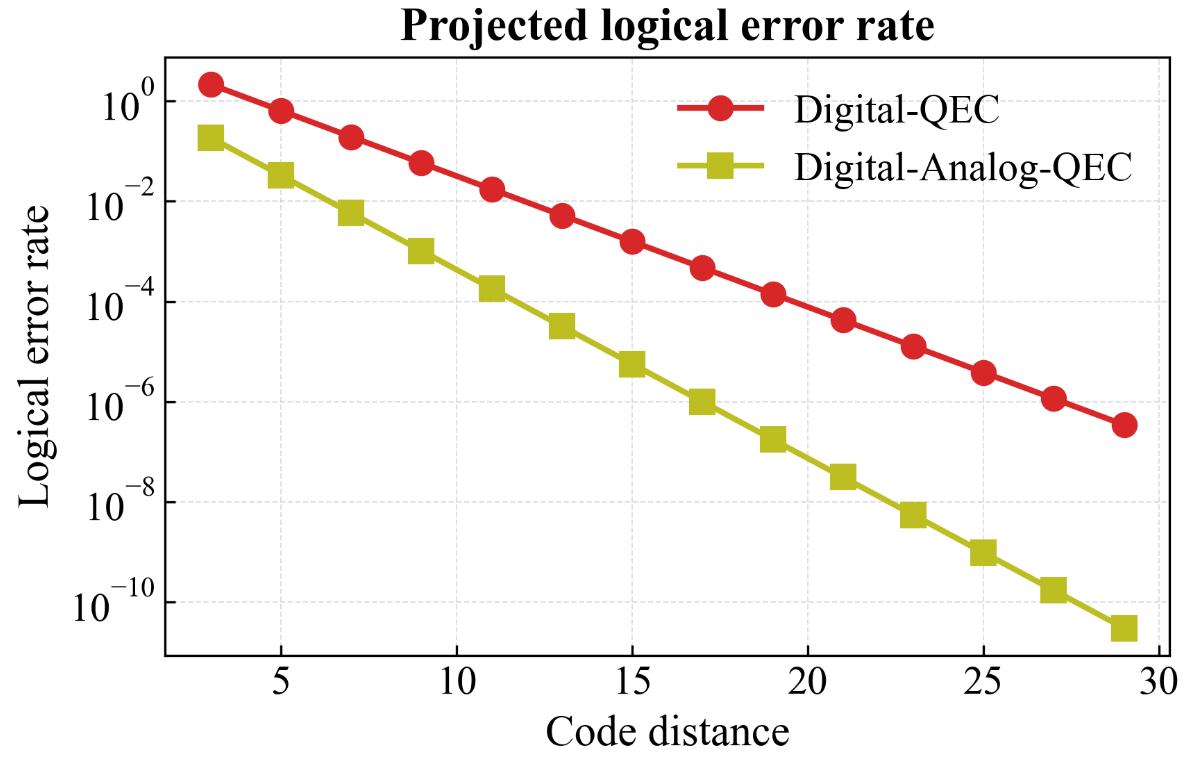

As shown in Fig. 3, DAQEC achieves an exponential suppression of logical error rates with increasing code distance. For example, at distance d=5, DAQEC yields a logical error rate approximately 32× lower than its digital counterpart, demonstrating a dramatic reduction in Logical error rate. This gap widens with code distance, meaning that for any given target logical error rate, DAQEC enables the use of smaller code distances, fewer physical qubits, and shallower circuits.

For example, with Kipu’s DAQEC one can achieve using a rotated surface code, a logical error rate of 10-3 with d=7 (49 physical qubits per logical qubit), whereas a Digital QEC scheme would require roughly d=10 (100 physical qubits per logical qubit). This leads to an observed roughly 2× (50 % less) fewer physical qubits per logical qubit. With the best encodings proposed (using 3-qubit CCZ gates), the maximum improvement achievable is 27% less physical qubits (see Hartmann et. al.).

This positions DAQEC as a hardware-specific QEC strategy that reduces both qubit and time budgets.

Why This Matters for Quantum Hardware Providers

A hardware-software co-design strategy is essential to unlocking the full potential of today’s quantum devices. With DAQEC, we offer a practical and hardware-native framework that significantly improves logical-qubit capacity per chip.In our benchmarking, we demonstrated that DAQEC can deliver the same logical error rate using only half the number of physical qubits compared to fully digital QEC meaning that on a fixed-size chip, twice as many logical qubits can be realized. This directly translates into 2× higher logical qubit density, which is critical for scaling in the NISQ-to-early-QEC transition.

DAQEC naturally aligns with the strengths of several quantum hardware platforms:

- Neutral-atom platforms: Can benefit from analog multi-qubit interactions (e.g., Rydberg-based entanglement) in DAQEC stabilizer preparation. QuEra has already demonstrated the applicability of analog multi-qubit interactions and digital gates for scalable error correction (see here)

- Superconducting qubits: Can use XY exchange interactions as entangling primitives for depth-efficient encoding.

- Trapped-ion systems: Can implement global multi-qubit gates such as Mølmer-Sørensen gate among other multi-qubit gates such as the XX or ZZ type to reduce the number of decomposed two-qubit gates (see DAQC in trapped-ions).

- Digital-analog native systems (e.g., D-Wave’s roadmap): Already structured to benefit from DAQC protocols for early surface-code deployment.

By integrating DA-QEC principles, hardware teams can demonstrate early-QEC with reduced system demands, within current hardware specs.

Hardware Momentum You Can Leverage Today

At Kipu Quantum, we are developing simulation frameworks tailored to DAQC compatible architectures such as superconducting circuits, neutral atoms and trapped-ions. These are not abstract models, they are optimized for the hardware constraints that today’s platforms face.

We are currently partnering with hardware providers to:

- Validate logical qubit preparation speeds using DAQC encodings

- Optimize stabilizer measurement cycles for minimal decoherence

- Quantify error suppression scaling with reduced-depth protocols

- Co-develop hardware-native error correction stacks

If you’re building the next generation of quantum processors, we’d invite to collaborate on deploying DAQEC on your platform.

Reach out to us. Let’s accelerate early quantum error correction together.